## JAK?

- Top-down, czyli (nano)technologia

- Bottom-up, czyli samoorganizacja

## **CO**?

- Studnie, druty, kropki

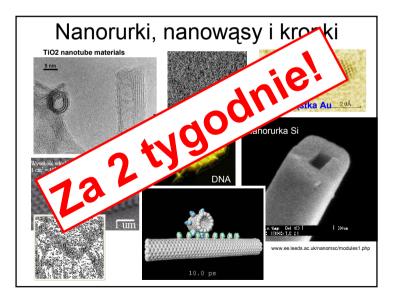

- Nanorurki i nanomaszyny

|                 | Gdzie jest limit                                                                                                                                                                                                                                                                                                |

|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                 | World - Press Release - Mozilla Firefox<br>Prestji Załładki Narzędzia Pomog<br>3) 😚 🗋 http://www.samsung.com/PressCenter/PressRelease/PressRelease.asp?seq=20050912_0000192003                                                                                                                                  |

| SAMSUNG         | PRODUCTS SUPPORT FEATURES PRESS CENTER ABOUT SAMSUNG Select Country / Region V                                                                                                                                                                                                                                  |

| PRESS CENTE     | R V PRODUCT REGISTRATION # COMMUNITY X CART - SEARCH                                                                                                                                                                                                                                                            |

| Press Release   | Home > Press Center > Press Release<br>Press Release                                                                                                                                                                                                                                                            |

| News Archive    |                                                                                                                                                                                                                                                                                                                 |

| Photo Archive   | 2005 🔽 💿                                                                                                                                                                                                                                                                                                        |

| Corporate Films | (12, Sep. 2005 / SEC)                                                                                                                                                                                                                                                                                           |

| Executive Bios  | <ul> <li>SAMSUNG Electronics Develops First 16-Gigabit NAND Memory Using</li> </ul>                                                                                                                                                                                                                             |

| PR Contacts     | 50-nm Technology for Sharp Jump in Mobile Storage Capacity                                                                                                                                                                                                                                                      |

|                 | Seoul, Korea, Sept ember 12, 2005 – Samsung Electronics Co. Ltd., the world leader in advanced memory technology,<br>announced that it has developed the world's highest density NAND flash – a 16Gigabt (Gb) NAND memory device. NAND is<br>the most widely used memory for multi-feature mobile applications. |

|                 |                                                                                                                                                                                                                                                                                                                 |

|                 |                                                                                                                                                                                                                                                                                                                 |

|                 |                                                                                                                                                                                                                                                                                                                 |

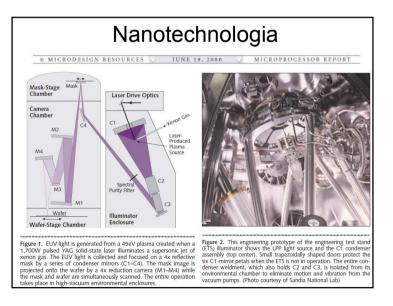

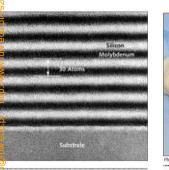

gare 5. Each of the seven normal-incidence mirrors (including the task) in the TTS is coated with 40 blayers of molybdenum and silcon are  $\lambda/2$  (30 atoms) thick, creating a distributed Bragg reflector. (a) reflectance at 13.5mm is 70%. (Source: Lawrence Livermore Lab)

Flot by Keth Dieferdoff

Figure 7. This photograph shows a polished and coated M4 mirror from the ETS camera. For people who appreciate ultrahigh precision, the mirror is a thing of beauty.

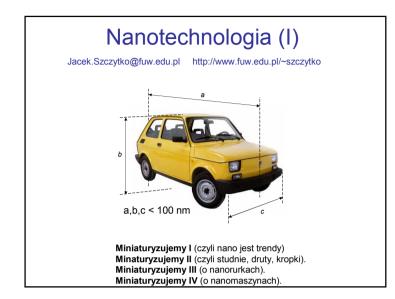

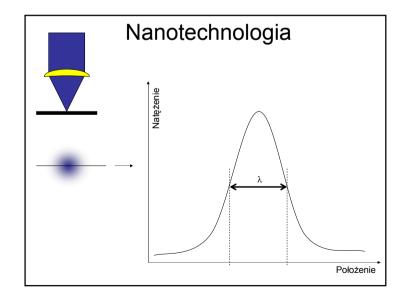

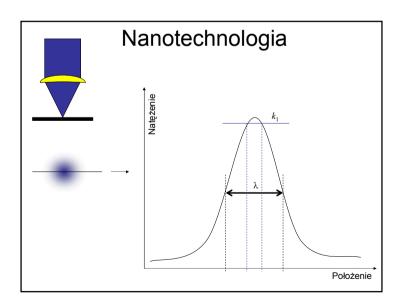

Nanotechnologia

| Nanotechnologia<br>Some Mask-Making Metrics and Comparisons                                                                  |                                |  |  |  |

|------------------------------------------------------------------------------------------------------------------------------|--------------------------------|--|--|--|

|                                                                                                                              |                                |  |  |  |

| –On a 90 nm technology node mask:<br>–In a high quality digital photo:                                                       | 1,000,000,000,000<br>4,000,000 |  |  |  |

| •Defects:                                                                                                                    |                                |  |  |  |

| -Size that must be found and repaired                                                                                        | 0.1 micron                     |  |  |  |

| -Number of such defects allowed:                                                                                             | 0                              |  |  |  |

| -Size ratio: defect to the mask area:                                                                                        | size of a basketbal            |  |  |  |

| •Data                                                                                                                        | area of California             |  |  |  |

| -Typical number of mask layers for 90 nm                                                                                     |                                |  |  |  |

| generation logic product:                                                                                                    | 22—25                          |  |  |  |

| <ul> <li>Total file size needed to specify all these layers:</li> <li>Time to transmit (design site to mask shop)</li> </ul> | 200 GB                         |  |  |  |

| using T1 line (1.4 MB/sec):                                                                                                  | ~1.5 days                      |  |  |  |

| -Time using T3 line (40 MB/sec):                                                                                             | ~1.5 hours                     |  |  |  |

| •Cost                                                                                                                        |                                |  |  |  |

| –Cost to lease a T3 line:<br>–Capital cost to build a 90 nm node capable mask                                                | \$70K/month                    |  |  |  |

| shop (capacity of 200 sets/year @50-70% yield):                                                                              | \$200-250M                     |  |  |  |

| Yearly cost to operate such a shop:    Cost to make a 90 nm node mask set                                                    | \$60-100M                      |  |  |  |

| (depreciation, labor, etc):                                                                                                  | ~\$800K-1.3M                   |  |  |  |

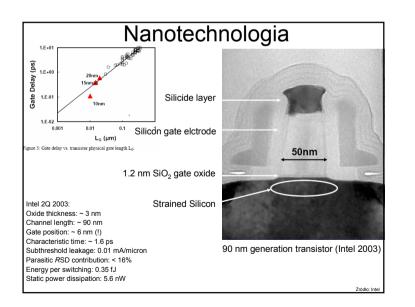

|                     |                        | st limit<br>oblems             | N/N/N |

|---------------------|------------------------|--------------------------------|-------|

| FEATURE             | LIMIT                  | REASON                         |       |

| Oxide Thickness     | 2.3 nm                 | Leakage (I <sub>GATE</sub> )   |       |

| Junction Depth      | 30 nm                  | Resistance (R <sub>SDE</sub> ) |       |

| Channel Doping      | V <sub>T</sub> =0.25 V | Leakage (I <sub>OFF</sub> )    |       |

| SDE Under Diffusion | 15 nm                  | Resistance (R <sub>INV</sub> ) |       |

| Channel Length      | 0.06µm                 | Leakage (I <sub>OFF</sub> )    |       |

|                     | 0.10µm                 | Leakage (IOFF)                 |       |

| Nanotechnologia<br>Some Mask-Making Metrics and Comparisons                                                                  |                                         |  |          |

|------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|--|----------|

|                                                                                                                              |                                         |  | •Pixels: |

| On a 90 nm technology node mask:<br>In a high quality digital photo:                                                         | 1,000,000,000,000<br>4,000,000          |  |          |

| •Defects:                                                                                                                    |                                         |  |          |

| -Size that must be found and repaired<br>-Number of such defects allowed:<br>-Size ratio: defect to the mask area:           | 0.1 micron<br>0<br>size of a basketball |  |          |

| •Data                                                                                                                        | area of California                      |  |          |

| <ul> <li>Typical number of mask layers for 90 nm<br/>generation logic product:</li> </ul>                                    | 22—25                                   |  |          |

| <ul> <li>Total file size needed to specify all these layers:</li> <li>Time to transmit (design site to mask shop)</li> </ul> | 200 GB                                  |  |          |

| using T1 line (1.4 MB/sec):                                                                                                  | ~1.5 days                               |  |          |

| -Time using T3 line (40 MB/sec):                                                                                             | ~1.5 hours                              |  |          |

| •Cost                                                                                                                        |                                         |  |          |

| –Cost to lease a T3 line:<br>–Capital cost to build a 90 nm node capable mask                                                | \$70K/month                             |  |          |

| shop (capacity of 200 sets/year @50-70% yield):                                                                              | \$200-250M                              |  |          |

| -Yearly cost to operate such a shop:<br>-Cost to make a 90 nm node mask set                                                  | \$60-100M                               |  |          |

| (depreciation, labor, etc):                                                                                                  | ~\$800K-1.3M                            |  |          |

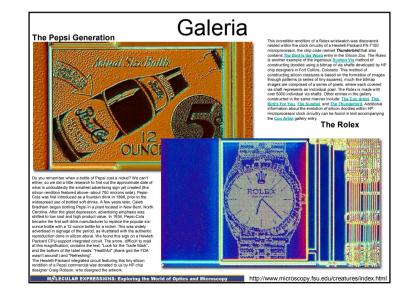

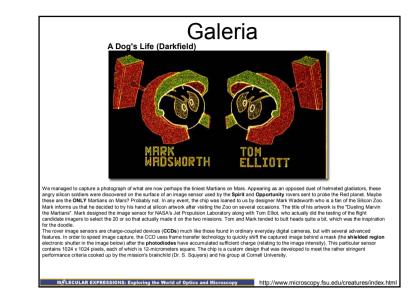

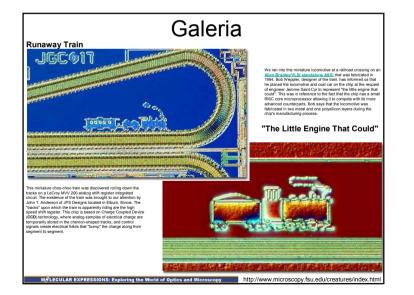

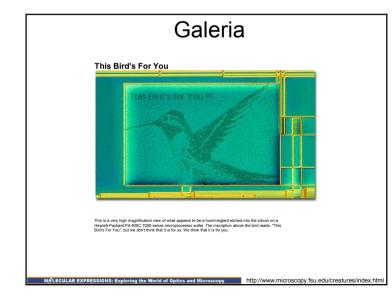

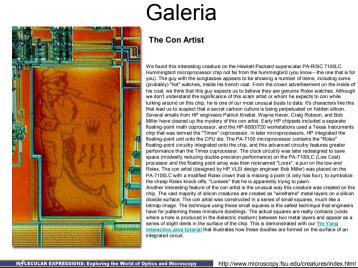

## The Con Artist

We found this interesting creature on the Hewlett-Packard superscalar PA-RISC 7100LC Hummingbird microprocessor chip not far from the hummingbird (you know--the one that is for Hummingoir microprocessor cnip not rar from the nummingoiro (you know-me one that is for you). The guy with the sunglasses appears to be showing a number of items, including some (probably) 'hot' watches, inside his trench coat. From the crown advertisement on the inside of his coat, we think that this guy expects us to believe they are genuine Rolex watches. Although we don't understand the significance of this scar and ist or whom he expects to con while we dorfur undright chipsgificance of this scara artist whom he expects to con while lurifing around on this chip, his is one of our most unusual busits to date. It's characters like this that lead us to suspect that ageners Patrick (Khebel, Wayne Kever, Craig Robson Hofen alloco Several emails from Her ageners Patrick (Khebel, Wayne Kever, Craig Robson and Bob Miller have cleared up the mystery of this scale. Early Her Aboption and a separate host and pace scales and the HP-9000720 works used a Texas Instruments chip that pace that more clearsor, and the HP-9000720 workson used a Texas Instruments chip that pace that The CPU de. The PA-2000 microprocessors, Hip the Robet for host and the CPU de. The PA-2000 microprocessors, Hip the Robet for host and the CPU de. The PA-2000 microprocessors, Hip the Robet for host and the CPU de. The PA-2000 microprocessors, Hip the Robet for host and the CPU de. The PA-2000 microprocessors, Hip the Robet for host and the CPU de. The PA-2000 microprocessors, Hip the Robet for host and the CPU de. The PA-2000 microprocessors, Hip the Robet for host and the CPU de. The PA-2000 microprocessors, Hip the Robet for host and the CPU de. The PA-2000 microprocessors, Hip the Robet for host and the CPU de. The PA-2000 microprocessors, Hip the Robet for host and host floating-point circuitry integrated onto the chip, and this advanced circuitry features greater performance than the Timex coprocessor. The clock circuitry was later redesigned to save space (modestly reducing double-precision performance) on the PA-TIOLC (Low Cost) processor and the floating point array was then nicknamed "Lorex", a pun on the low-end Rolex. The con artist (designed by HP VLS) design engineer Bob Miller) was placed on the PA-7100LC with a modified Rolex crown that is missing a point (it only has four), to symbolize the chean Rolex knock-offs "Lorexes" that he is apparently trying to nawn the cheap rouse whoevers, coreces viat net a paperainty ying to pain. Another interesting feature of the con artist is the unusual way this creature was created on the chip. The vast majority of silicon creatures are created as "wireframe" metal layers on a silicon dioxide surface. The con artist was constructed in a series of small squares, much like a bitmap image. The technique using these small squares is the safest technique that engineers have for patterning these miniature doodlings. The actual squares are really contacts (voids where a hole is produced in the dielectric medium) between two metal layers and appear as a series of slight dents in the surface of the chip. This is demonstrated with our <u>Fin Yang</u>